What is RISC-V and what does it mean for Android and Wear OS?

The future is both minimal and customized.

Qualcomm has announced that it's working with Google to develop a custom Wear OS platform using the RISC-V ISA. We already knew Qualcomm was investing heavily into advancing the use of RISC-V with the formation of RISE in early 2023. Qualcomm even started a new company with Bosch, Infineon, Nordic Semiconductor, and NXP to further the availability of commercial products using the RISC-V ISA. The biggest players in the industry working together means future generations of devices will be based on this platform.

But what is RISC-V? What exactly is an ISA? What does any of this mean for the people who use Android and Wear OS, like you and me? Spoiler: it's really cool stuff.

What is RISC-V?

RISC-V is an open-source ISA (Instruction Set Architecture) used for the development of custom processors. It's based on the RISC (Reduced Instruction Set Computing) computer architecture and provided under royalty-free open-source licensing by RISC-V International, a Swiss nonprofit.

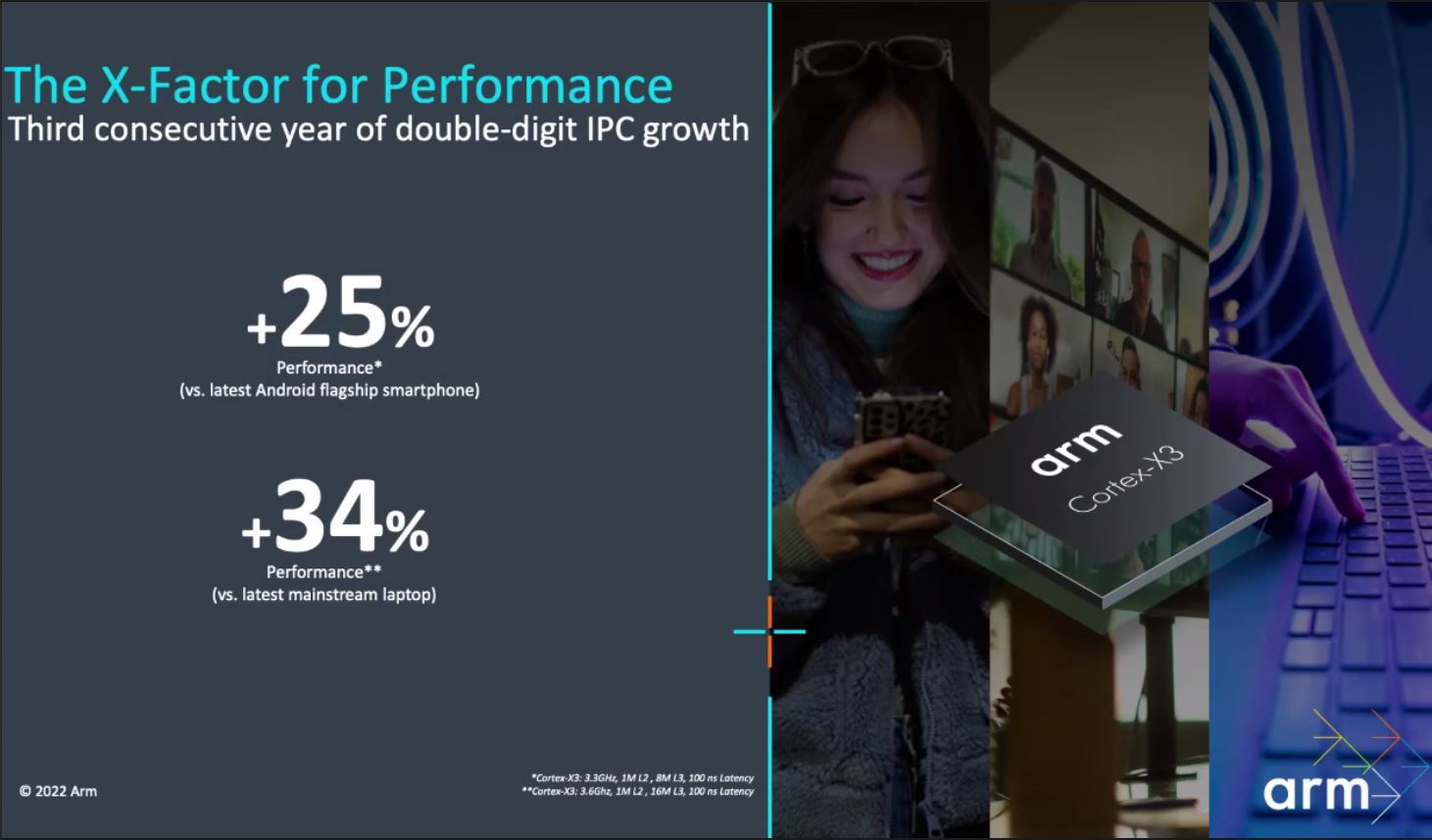

The RISC ISA uses the concept that each instruction given to a processor should only perform one function. To do more, you simply send more instructions. By keeping instructions that are done locally on the processor, like math, separate from instructions that use other parts of a computer, the time needed to do a task is easy to predict, and the overall design is simplified. Compared to a CISC (Complex Instruction Set Computer) design like ARM, the platform used in things like your phone or your smartwatch, a RISC processor needs more individual instructions, but each is done very fast.

A RISC processor requires more individual instructions than an ARM processor, but they're done faster and more efficiently.

That's a lot of acronyms and a complicated overview of something that's actually a simple idea: doing small things one at a time very quickly can be more efficient than doing one complicated thing sometimes. Both deliver the same result as far as a user is concerned, so the focus is on efficiency.

Both RISC-V computing and CISC-based ISAs, like ARM, have strengths and weaknesses. ARM is very power efficient, highly scalable, and has a mature, stable ecosystem. Right now, it's the ideal platform for small embedded devices, which is why there are hundreds of billions of them out there. That may change in the near future because of the things that make RISC-V great.

What makes RISC-V important for you?

There are a few reasons why companies like Qualcomm, Google, NVIDIA, and more are interested in RISC-V, but there are two really important ones: its openness and its modularity.

Get the latest news from Android Central, your trusted companion in the world of Android

RISC-V is provided under lenient and royalty-free open-source licensing. That means companies are free to take it, modify it to better suit a particular need, and build devices using these designs. The next company can reference these to make it even better. Corporations can even work together without waiting for a company like Arm or Intel to develop the "next generation" of processor core design. Ideally, RISC-V's open-source nature will encourage collaboration and innovation.

RISC-V is also really modular. The base ISA can power everything from a simple single-purpose controller to a full mainframe supercomputer through the use of extensions. That means high-level software like an operating system is easier to develop and maintain because no matter what company develops a RISC-V processor, the code is the same.

When you combine all of this, things get really interesting. A company can develop a custom processor designed for specific tasks that are tailored for a targeted set of end-use applications. An optimized PPA (power, performance, and area) built on a platform where each feature can be hand-picked will be far more flexible than having to use the full feature set, and that means better performance using less power.

Simply put, the development of RISC-V means your smartwatch — and eventually your phone — will be faster and actually have better battery life once all the quirks are worked out. I've written about how the Tensor G3 is so great because of the custom design of both hardware and software tailored for Google's AI code. Take that idea and extend it to the whole chip, designed to be really good at Wear OS things or Android phone things.

We're not there yet, and it's a big hill to climb. ARM designs are used today because they are so good where it matters. RISC-V designs may not ever catch up. If they do, we can finally expect a device that's as good as the company selling it claims when it comes to performance and efficiency.

Jerry is an amateur woodworker and struggling shade tree mechanic. There's nothing he can't take apart, but many things he can't reassemble. You'll find him writing and speaking his loud opinion on Android Central and occasionally on Threads.